AMD had been down this road before. In 2003, the chip maker launched the “SledgeHammer” Opteron, the first 64-bit X86 server processor with backward compatibility to its 32-bit predecessors that came at a time when much larger rival Intel was still pumping up Itanium as the next-generation architecture – and its only 64-bit option. In a short three or so years, AMD held more than 20 percent of the server chip market and had assumed the role of a serious competitor to Intel.

However, a combination of missteps and missed deadlines by AMD in the following years and an awakened Intel that quickly shifted is massive reserves of resources into eliminating any advantage the Opteron may have had made AMD decide to wandering out of the datacenter. There were still Opteron chips coming out and some side projects like an Opteron A110 chip, code-named “Seattle,” but a good amount of discussion in the industry was around trying to guess which IT company would eventually buy AMD and sell it for parts.

Given all that, it was understandable that when AMD officials a few years ago began talking about a new, built-from-the-ground-up microarchitecture called Zen that would form the foundation of its new processors – not only for servers but also for client systems – there was skepticism among system makers as well as their customers and partners. Promises of significant performance and efficiency gains and reduced operating costs only upped the pressure on the chip maker, leading many to say that if AMD had any chance at remaking any inroads into a server market that was rapidly changing but still dominated by Intel, it had to execute on the first generation of its Zen-based Epyc chip – code-named “Naples” – and convince a wary industry that it was capable of continuing any momentum gained by creating future versions that were marked improvements and on time.

That’s what AMD did. Naples came out on time in 2017 and delivered on the extensive promises president and chief executive officer Lisa Su, chief technology officer and executive vice president Mark Papermaster, and other executives had made. At the same time, they spoke about a development process of leapfrogging teams, where one would work on one generation of the chip and while another group worked on the following generation. The process was designed to ensure that the product roadmap was met.

At the launch event this week in San Francisco for the second-generation Epyc processor – dubbed “Rome” – Su and others were clear that they understood how important it was for Naples to succeed, for Rome to be a significant upgrade over Naples, and for the company to show that the roadmap was still on schedule for the upcoming iterations. Doing all this would give OEMs and their customers confidence that AMD not only could develop good server chips but would be able to do so in the years to come.

“It is not about one generation. It’s not about two generations,” Su said during her keynote address. “We are committed to this space.” Papermaster said it was important for AMD to be seen as a “fully bankable supplier of X86 processors,” adding during a session with analysts and journalists that when AMD began talking about Zen and Naples, the response from many in the industry was, “’I got that, but I’ve seen that from AMD before. Even if you do it, how are you going sustain it?’ Our journey from the outset was about that. Will AMD be that enterprise, that credible supplier of X86, generation in and generation out? We want to put that rest and it will be removed from the dialogue as we stay heads down and focused on execution.”

With Naples, OEMs and some cloud service providers rolled out a few systems and instances powered by the chips to be used by customers that were curious about the AMD processors but were cautious about going too far in on a first-generation product from a company that not too long before was dogged by execution issues. However, Naples’ capabilities, improvements in Rome and AMD’s ability to follow through on promises and roadmaps convinced hardware partners and customers alike that AMD may be worth a greater look and that was put on display during the event for Rome.

AMD noted during the Rome event that it already is looking to generations down the road, with deign for the third generation “Milan” being completed and fourth-generation Genoa entering the design stage.

The Next Platform has done a detailed analysis of the Rome Epyc server chip family and is working on a deeper dive into its architecture, which will publish shortly, but OEMs at the event pointed to such features as support for PCI-Express 4.0, 64 Zen 2 CPU cores (twice that of Naples), an enhanced Infinity Architecture, four times the L3 cache, 24 slots for NVM-Express storage devices and greater security as key features that enable Rome to have twice the performance of its predecessor, more than twice the performance per dollar, 40 percent to 50 percent lower operating costs and better performance than Intel 14 nanometer “Cascade Lake” Xeon SP processors.

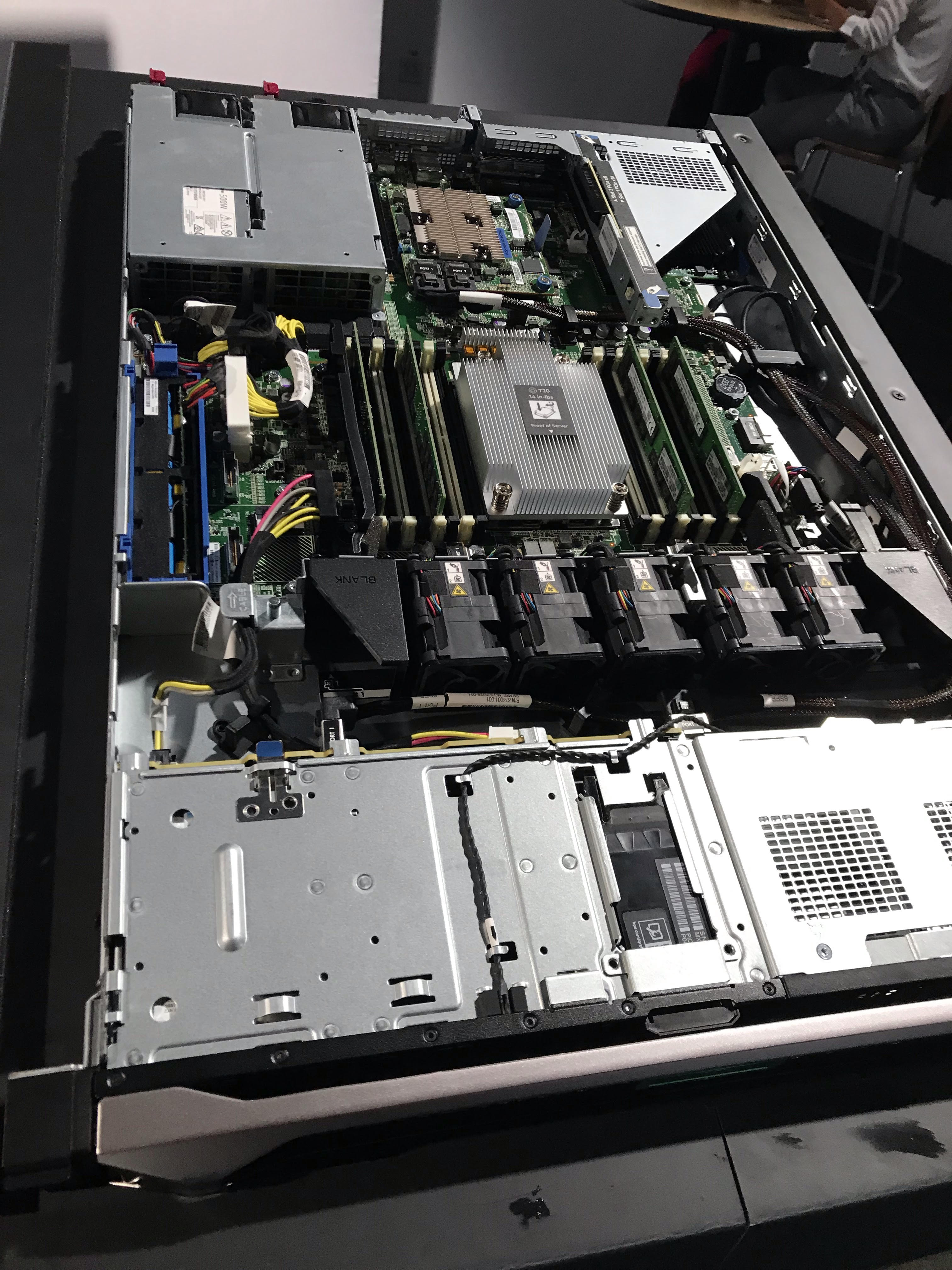

Lenovo focused on HPC and cloud solutions with Naples, but now is rolling out two one-socket servers – the ThinkSystem SR635 and SR655 (below) – powered by the Epyc 7002 Series chips and aimed at emerging enterprise workloads like video surveillance, edge applications and virtualization. The OEM also plans to put Rome into its vSAN ReadyNode hyperconverged solutions.

“At that time, we saw what they were doing in the second generation and that’s when we decided to do something beyond just those areas,” Doug Fisher, COO and senior vice president of business units for Lenovo’s DCG Solutions, told journalists at a roundtable discussion. “It was the platform roadmap they showed us and we decided that was the right way to invest, to put it into enterprise space this time.”

Scott Aylor, corporate vice president and general manager, AMD datacenter solutions, said Lenovo with Naples was very focused on hyperscalers in China like Baidu and Tencent, but that Lenovo is “excited to be expanding into the more traditional, mainstream enterprise. That also says that we’ve done what we said we’d do, we earned their trust, we’re expanding the portfolio in this generation and we have a vision to expand further.”

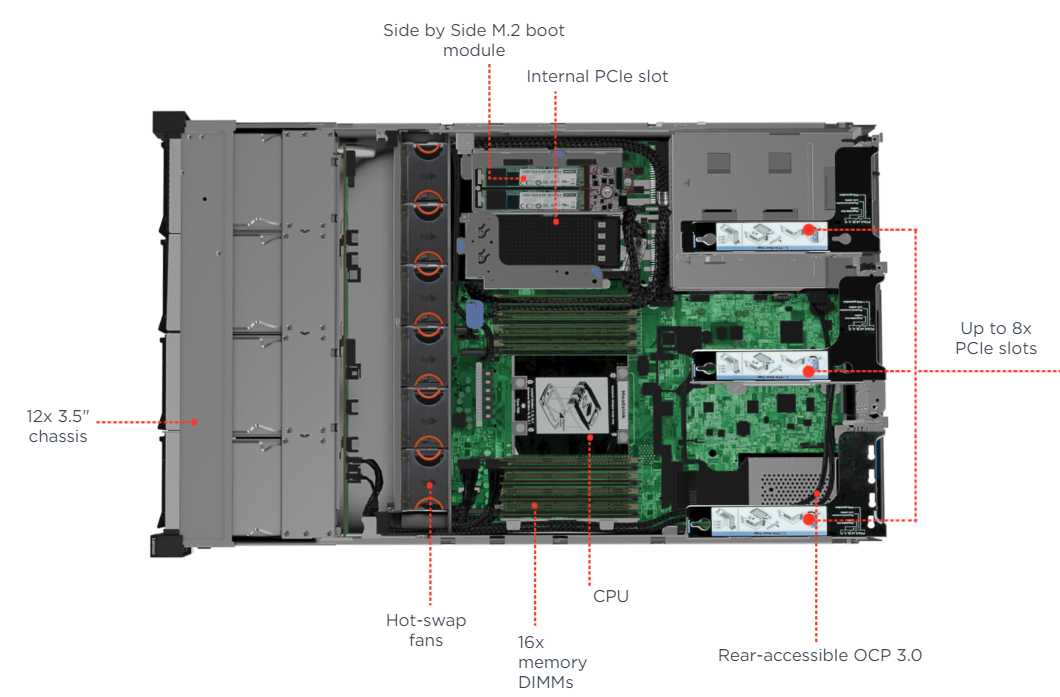

The story was similar with other system makers. Wary customers got a chance to try out Naples and saw the roadmap AMD has for Epyc and the roadmap the OEMs have for the chip, all of which convinced them to ask the vendors for more Epyc-based offerings. Hewlett Packard Enterprise offers Naples on four servers – the ProLiant DL325 (below) and DL385, the Apollo 35 and the Cloudline CL 4150. The company is putting Rome into the ProLiant and Apollo systems and by this time next year will have the second-generation Epyc in as many as a dozen HPE systems.

Dell EMC similarly is expanding its lineup of Epyc-based offerings beyond the three servers – the PowerEdge R6415, R7415 and R7425 – that currently are available with Naples. The company will give more details when the Rome-based systems – which will include one- and two-socket servers – are released in the fall, according to Ravi Pendekanti, senior vice president of server solutions product management and marketing at Dell.

“With the first-generation Naples platform, there was a lot of curiosity and a lot of interest, and we believe with the second-generation of Epyc, we’ll see a lot more interest from our customers,” Pendekanti tells The Next Platform. “They have seen one generation, so with the second generation, they feel like, ‘Well, we’ve had a chance to check it out and understand it better.’ So we feel good about what this can do for the industry in general.”

Tom Lattin, vice president and general manager of ProLiant and Cloudline systems at Hewlett Packard Enterprise, says there was “uncertainty among customers about how committed AMD was [with Naples] and quite frankly how committed HPE was to an AMD-based roadmap. But for those customers who were able to actually complete an evaluation of those products, we saw a strong uptake of both the two ProLiants systems, and in particular the ProLiant DL325.”

That was because the ProLiant DL325 gave enterprises two-socket performance in a single-socket system, offering greater economics around pricing and licensing costs for such workloads as analytics and virtualization. That’s a theme AMD hit hard during the Rome event, that single-socket systems powered by the new Epyc processors will be able to run essentially every two-socket workload as well or better than dual-socket servers from Intel.

The focus by enterprises on workload optimization of systems was a key part of the discussion about Rome. Pendekanti said that “when talking to our customers, they’re not looking just at benchmarks. What they look to do is focus on specific workloads because every workload is different. Given that, we are definitely deepening and expanding our relationship with AMD.”

“The customer segments that have snapped to the Rome value proposition are the ones where it’s so compelling that it can’t be ignored,” Lattin tells The Next Platform. “High performance computing is one of those, high-performance data analytics environments, virtualization for sure. Those customers in those spaces bring the dialogue to us and say, ‘I can’t ignore this, so I need to know what the rest of your roadmap looks like so I can gain confidence that I’ve got some longevity on my planning based on this.’”

Original design manufacturer Quanta Computer can custom build Naples-based servers upon request, but this year the company will launch five Rome-based systems aimed at cloud service providers, including the QuantaGrid D43K (below), a 1U system with two Epyc chips and up to five expansion slots for PCIe Gen 4.0. Cloud service providers like Google are seeing that value in getting twice the performance from the Epyc 7002 chips, driving Quanta’s decision to produce these systems, Michael Quan, director of sales engineering, tells The Next Platform.

AMD also is seeing expanded support among cloud providers. Microsoft Azure currently offers VMs for HPC and storage workloads in its HBv1 and Lv2 instances. During the event, Girish Bablani, corporate vice president at Azure, said the cloud provider will offer Azure VMs for HPC, virtual desktop, memory-intensive and general-purpose workloads. Meanwhile, Bart Sano, vice president of engineering at Google, announced it has deployed Rome processors in its internal datacenters and later this year will offer general-purpose machines powered by the new processors on the Google Cloud Compute Engine.

On stage with Su, Sano noted the growing need for more speed, scalability, and throughput to run hyperscale applications in Google’s datacenters while keeping a lid on TCO, all of which he said is addressed by the new Epyc chips.

Twitter also will deploy Rome chips in its datacenter infrastructure this year, reducing TCO by 25 percent, which will allow for more compute capacity in the same datacenters, according to Jen Fraser, senior director of engineering with the social media giant. The reduced amount of power for each Rome core means 40 percent cores in each rack with the same power and cooling.

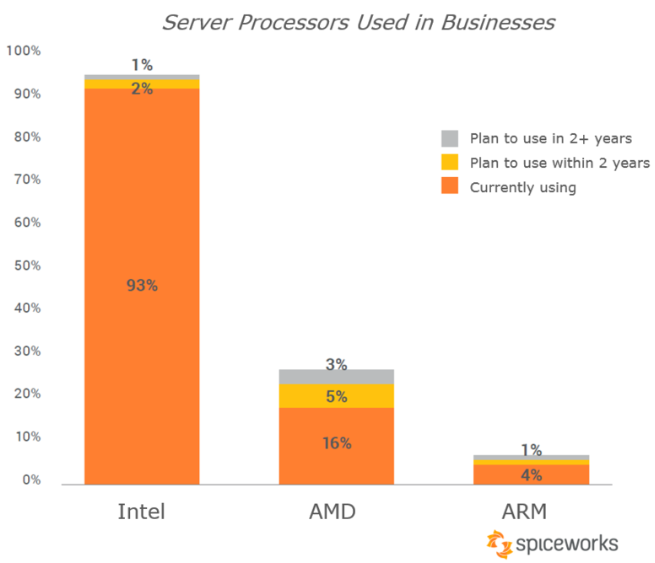

The success of Naples has given AMD traction in the server space that the company hopes Rome will enable it to grow on. AMD’s Aylor said that in the two-socket server space, the chip maker held about 4 percent of the market at the end of last year and hopes to reach double-digit market share within the next four to six quarters.

Others also are seeing growing use of AMD chips in datacenters. According to a report in May by Spiceworks, 93 percent of organizations use Intel chips in their servers, while 16 percent use AMD processors. Spiceworks expects the adoption of AMD server chips will reach 21 percent within the next two years.

Four percent of organizations run some of their infrastructure with servers based on Arm chips. This sounds a bit high, based on the market data that we have seen.

On August 5, 2019, AMD share of 14/12 nm commercial server/workstation/communications control plane market is 1.25%, and 4.4% of all 14/12 nm desktop/notebook. By product category and grade SKU v Intel AMD product market share results increase. For example in relation Xeon W, AMD TR holds 100% share.

How about TNP presenting 1P Epyc 7742 v 4-way Xeon 5220_ and E7 4850 v4 review?

No media site appears interested in 1:1 core performance purely apples and oranges component cores comparison within device power. No Media site appears interested in AMD v Intel actual commercial component price performance. How about lightweight VM v heavyweight MP on this platform review option?

Mike Bruzzone, Camp Marketing

I will add reflecting on Rome launch coverage, the most simple, direct, overlooked and or negated performance assessment worth doing were / are;

At 24 core relatively head to head comparison in relation to what was actually done;

XCL Gold 6252N 24C 2.1 to 3.6 GHz 35.75 MB L3 150w vs. Epyc Rome 7402 24C 2.8 to 3.35 GHz 128 MB L3, 180w

At 16 cores,

XCL Gold 5218T 16C 2.1 to 3.8 GHz 22 MB L3 105w vs. Epyc Rome 2782 16C 2.0 to 3.2 GHz 64 MB L3 120w

16 to 20 cores is the enterprise sweet spot.

We might have actually learned something architecturally.

Mike Bruzzone, Camp Marketing