When it comes to competition at the high end of the FPGA market, Xilinx and Altera (now part of Intel) are the two monolithic players, capturing the lions share of use cases. There are countless other FPGA companies that focus on the mid-range and low-end with a lower cost of entry to begin competing, but until recently, there has not been much momentum from the startup world to aggressively tackle the giants.

It is not cheap to come out swinging with a 7nm FPGA to take on certain high-value segments of the datacenter FPGA market, but Achronix is aiming at the heart of both Xilinx and Intel/Altera with its reveal today a product family that is exploiting some of the weaknesses of other devices and for that matter, the companies that make them.

Those chinks in the armor are especially clear on the Intel side as the company continues to form its strategy around where FPGAs will fit in key markets (autonomous, 5G, inference, network acceleration, etc.) inside the wide-ranging Datacenter Group at Intel where other acquisitions (Mobileye, for instance) shift focus on some workloads to other architectural approaches. Some have argued that the lack of focus at Intel has been great news for Xilinx, which continues to push an aggressive roadmap and secure some big wins.

There is value in that success for Xilinx, of course, and while they have continued to diversify their lineup to suit a wide range of use cases, the natural entry point for a high-end FPGA upstart is keeping a razor sharp focus on just a few workloads. That is exactly what Achronix has done, focusing its design, which does have some unique elements, around applications with some of the highest performance requirements.

Finding the weak points and designing architectures around those has been Manoj Roge’s specialty at both Altera and Xilinx over the years. He is now leading the charge into this high end market at Achronix and feels confident that the new product roadmap for high performance data acceleration with an FPGA device and IP licensing strategy for high volume will push them into more competitive territory.

Achronix is not necessarily a startup in the way we have known them in the chip space lately. They were founded in 2004, starting with asynchronous logic-based devices (hence their name) that focused on that unique technology before there was much of a market for it. These were very fast devices but required more power than customers were willing to spend on so they joined the mainstream with synchronous devices with Intel’s custom foundry at the core and moved from 22 nanometers and now are set to deliver a 7 nanometer product later this year.

Roge tells The Next Platform they have been cash flow positive since the end of 2016, which is about when they set to work on the forthcoming standalone Speedster devices, which we will provide a deeper architectural piece about later this week.

In terms of this high-end focus, he says that Intel/Altera are walking away from a number of markets. “They took a chiplet approach of bolting the SerDes chiplet onto the FPGA die, which will add latency to the transceiver paths. That means they are walking away from high frequency trading applications that need low latency. They’re also walking away from autonomous driving for the FPGAs with the Mobileye acquisition, which is being positioned for that workload. There are also a lot of industrial, aerospace, and defense applications left on the table.” He says Xilinx has had an excellent execution strategy in the way of this but that there is still a need for options.

“We focused on what we were good at; building high performance FPGAs. We could not do a me-too product. We have differentiation of our own. We believe in heterogeneous compute trends but we do not believe in putting everything on a single chip. It is too hard to get the balance right. We got that feedback specifically from the hyperscalers we have talked to.”

Roge says it was immediately clear integration was not a reasonable approach. Aside from the balance problem, it adds significant complexity. “The GPU analogy is a good one as plenty of companies have tried to integrate these and it just doesn’t work. The FPGA is an accelerator. We want to design a best in class FPGA as an accelerator and deploy on PCIe. Microsoft and Amazon do this already and there are plenty of ports to do so. We keep track of all of the interconnects and focus also on getting data directly on Ethernet,” he adds.

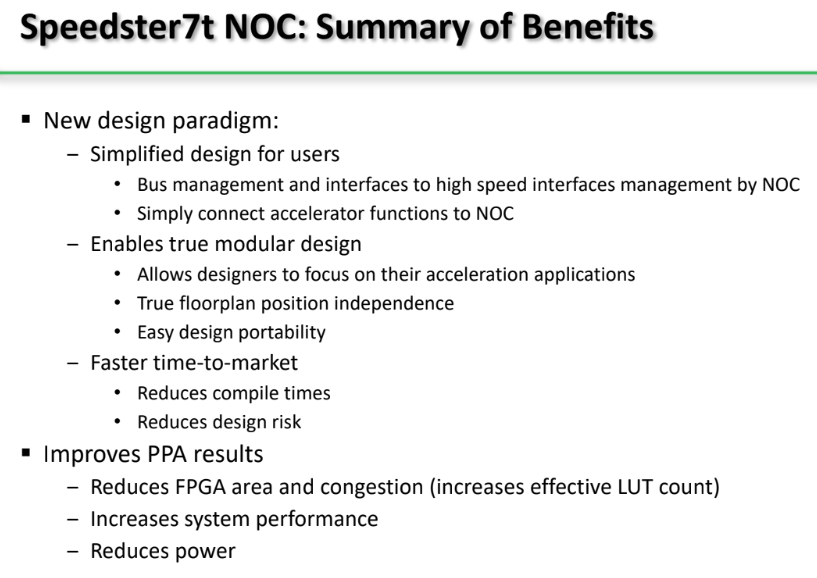

We have a separate architecture-focused piece for those interested in the finer details but in essence their technology strategy hinges on three basic foundations: efficient compute, the right memory hierarchy and bandwidth (starting with DDR for bulk external memory, GDDR for high-bandwidth memory and sufficient on-chip memory). They use a 2D network-on-chip that we will describe in more detail as well. “We took a blank slate approach since we were not burdened with many thousands of customers for our 22 nanometer product that is shipping. We looked at each block, particularly the DSP block, which has evolved over 25 years to suit the needs of wireless and radar type applications. We threw a lot of this out and designed the DSP block to be optimized for INT-8 teraops, which is relevant for inference and is fully programmable so it’s possible to go down to 4-bit, 2-bit, or binary.”

With this approach Achronix thinks it take on machine learning and network acceleration very well and branch out from there to other segments.

“In many years of FPGA planning, what typically happens is we get hundreds of use cases from all market segments and try to map those to one architecture. Maybe five or six of those tape out. By definition we had to have some kind of kitchen sink architecture to tackle wide business but we decided to excel in a few segments and make sure we’re optimized for data acceleration.”

Achronix has hedged against this reality at the mid-and low-end with their FPGA IP licensing strategy. This means they have two balanced bits of business—one to take on the high-end and one to feed to the low end if FPGA adoption grows but is quickly shuttled to ASIC. They are, from what we can see, the only company with standalone, embedded, and licensed product lines for that mid/low range and also for datacenter application acceleration (consider Amazon’s Inferentia engine, for instance—why buy when you can build?).

“Today not many businesses have deployed AI so we expect that there will be a hockey stick demand for AI Chips. Where FPGAs, play is that the algorithms keep evolving. People are also customizing the network. As all of this evolves we can enable that hardware flexibility. Add to that techniques like pruning and quantization in AI that deliver orders of magnitude more compute efficiency and we are enabling next generation of efficient inference.”

All of this seems to make good sense but it is still a big risk for a relatively small company. Achronix CEO, Robert Blake, tells us that moving to 7 nanometers with no expense spared on the long design road is a big step but they have solid technical expertise and a narrow market set to tackle. His years strategizing at Altera (and earlier LSI and Fairchild) give him and his company some insight that could actually push another viable player into the top tier of FPGA makers. We will certainly be watching this one. And if we had to make bets, there is no one in an FPGA acquisition mood that we can think of at this point in 2019.

Again, here is an architecture-centric piece that looks much closer at the NoC and why it matters:

Be the first to comment