Different workloads need different mixes of price, performance, thermals, and longevity in the field out there on the edge and in the datacenter, and that is why server CPU makers for years have had a mix of processors that deliver on these vectors that are different from each other.

What makes 2023 different from 2003 is that these differences in the salient characteristics and packaging of these processors is more explicit and arguably more rich. With today’s launch of the “Siena” Epyc 8004 processors, based on the Zen 4c cores, AMD has completed the set, and soon all attention will turn to the “Turin” Zen 5 generation due in 2024 and we are already hearing rumblings about the “Venice” Zen 6 that we expect in 2025.

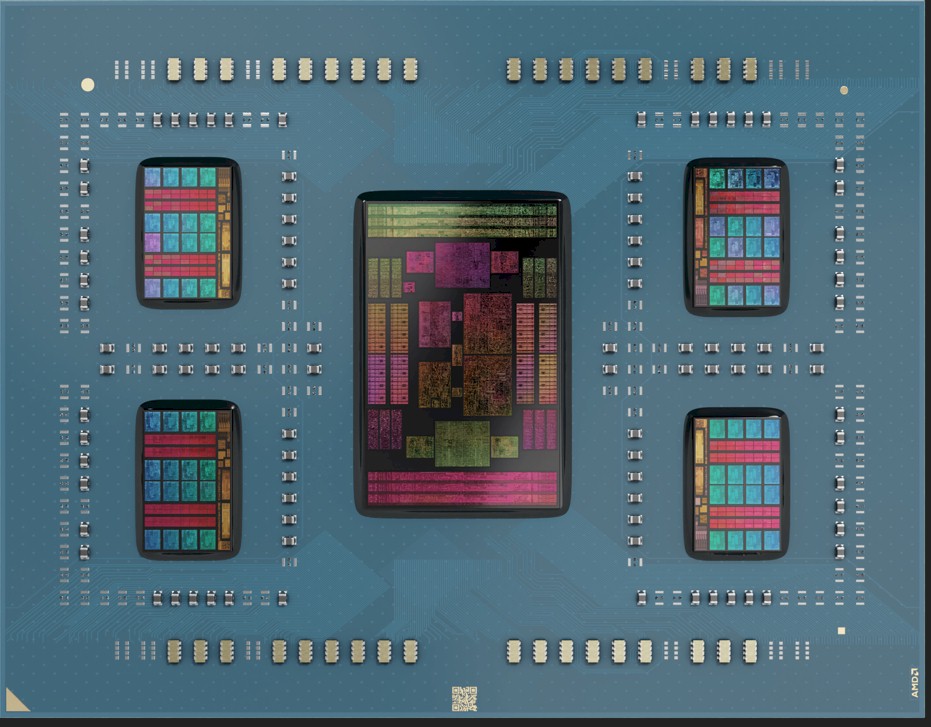

As we detailed back in June when the “Bergamo” Epyc server variants debuted with the Zen 4c cores, the basic difference between the Zen 4 and the Zen 4c core that the former has 4 MB of L3 cache per core and the latter cuts that back to 2 MB of L3 cache per core. The Zen 4c cores are about 35 percent smaller in the same 5 nanometer process from Taiwan Semiconductor Manufacturing Co, and that means AMD could create a compute complex die (CCD) with 16 cores on it based on Zen 4c cores rather than a CCD with eight cores on it used in the plain vanilla “Genoa” 9004 parts and their Genoa-X variants, which have 3D V-Cache to further boost their performance. The Genoa and Genoa-X chips had a maximum of a dozen of those eight-core CCDs for a maximum of 96 cores, but the Bergamo variants needed only eight of those 16-core Zen 4c CCDs to provide up to 128 cores on a single socket.

In the shift from Bergamo to Siena, you basically take half of the CCDs off the Bergamo complex and you allow a configurable thermal design point that has a wide range for normal use in a single socket server and then you also create a NEBS-compliant version for telco, service provider, and edge use cases that locks down the TDP and offers a wider thermal environment range and then charge a premium for that NEBS variant.

That, in a nutshell, is Siena.

This composite chart sums up the positioning of the four different Genoa-class AMD CPUs and how they compare to each other and Intel equivalents pretty succinctly:

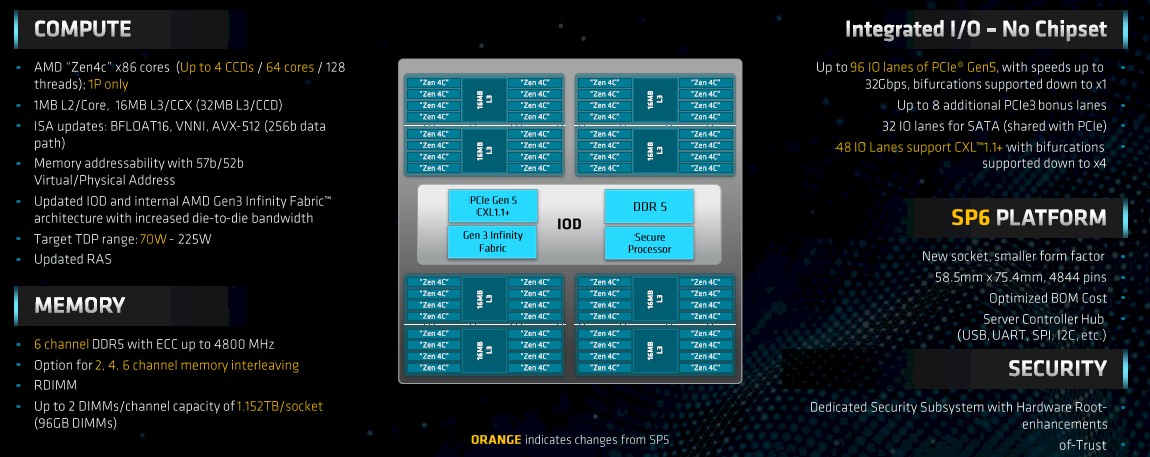

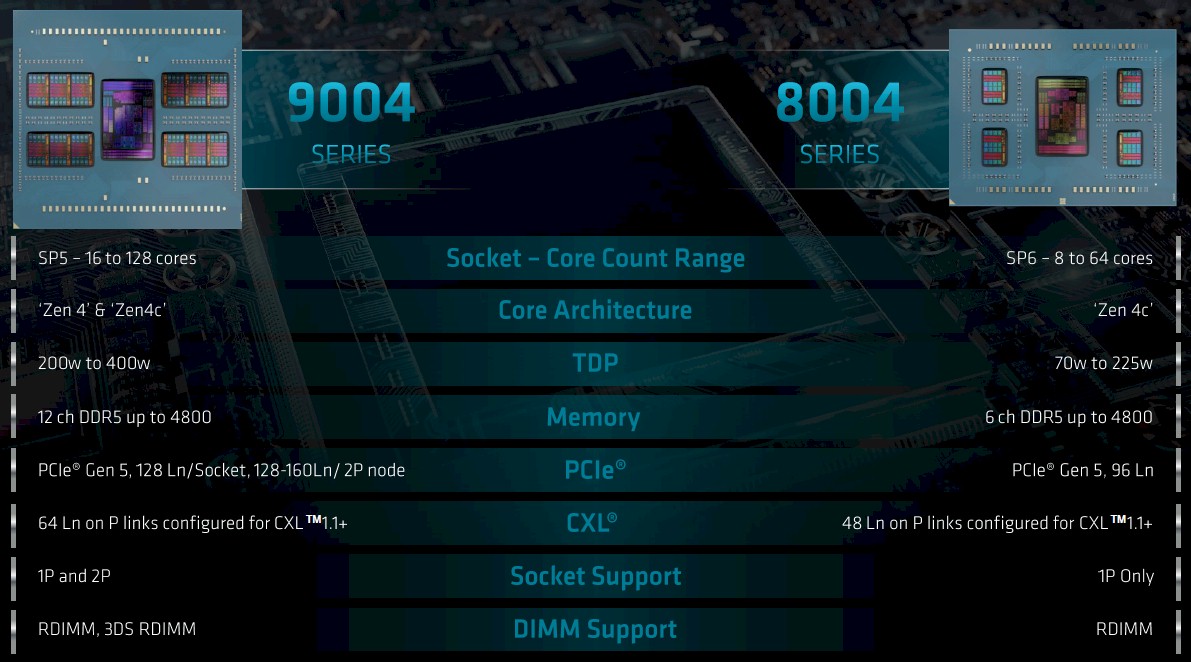

Another big change that comes with Siena is a new SP6 socket, which is optimized for lower power draw and lower thermals commensurate with it being basically a half of a Bergamo processor with a disproportionately lower cost:

The Siena chip has six DDR5 memory channels that run only up to 4.8 GHz in speed and offer up to 1,152 GB (the spec sheet above says 1.152 TB but that is wrong) of memory capacity per socket. (The spec sheet talks about using 96 GB memory sticks, and with two DIMMs per channel and six memory channels, you get 1,152 GB of memory total, which is 1.125 TB of memory. The Siena chip has 96 lanes of PCI-Express 5.0 peripheral capacity coming off that central I/O die, which is the same one used by the other Genoa, Genoa-X, and Bergamo processors. If you want CXL 1.1 memory coherency support with accelerators or DRAM memory extenders, you can use CXL on 48 out of those 96 lanes.

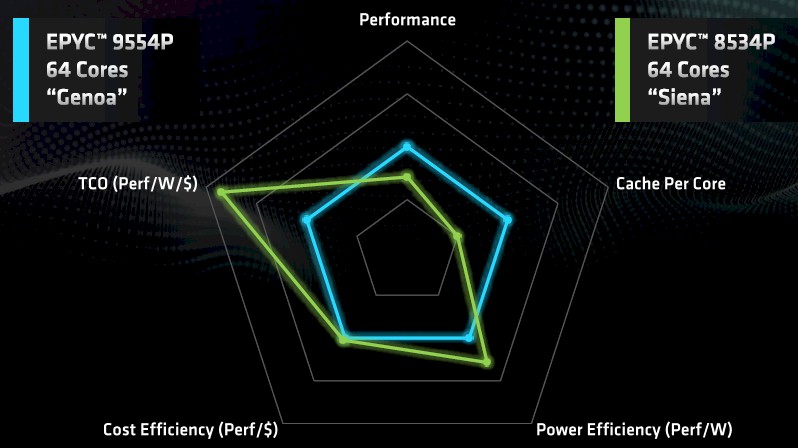

Here is the spider graph that shows you how the optimizations for Siena stack up against Genoa:

And here is a basic feeds and speeds comparison between Siera and Genoa:

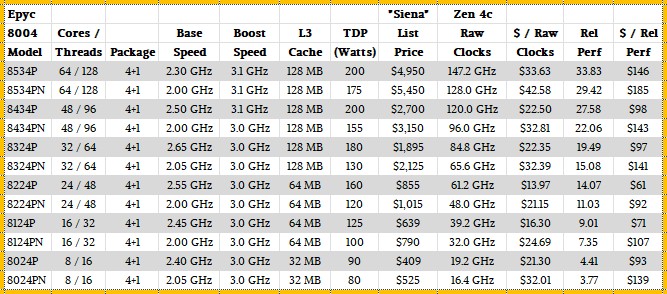

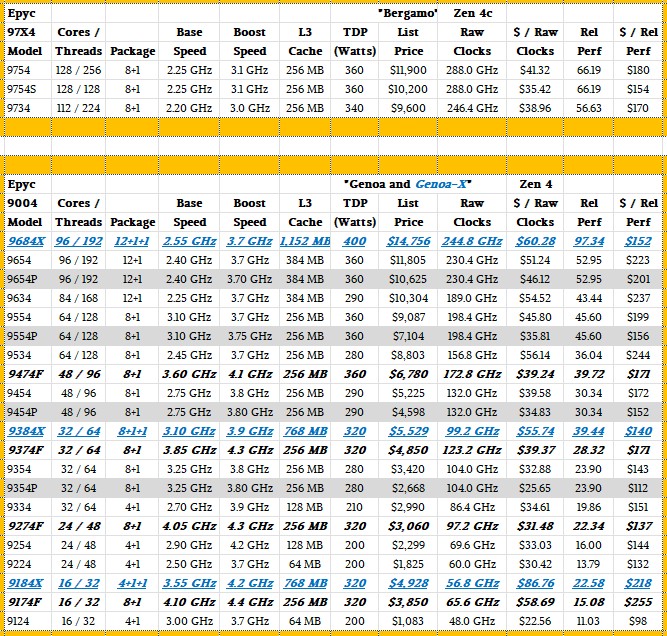

Without further ado, here is the SKU stack and pricing for the Siena chips:

And for reference, here are the SKU stacks and pricing for the Bergamo and Genoa/Genoa-X CPUs:

Incidentally, for both the Bergamo and Siena processors, AMD keeps saying that the ISA is exactly the same between the Zen 4 and Zen 4c cores and further that the instructions per clock (IPC) for the two cores are also the same. We believe the former, but we think it all depends on how you calculate the IPC on the latter.

We do not believe that on a mix of real-world workloads where IPC should be measured that IPC on Zen 4c is the same as Zen 4. But we think Zen 4c IPC might be a smidgen lower than Zen 4 IPC relative to Zen 3, but probably not a lot – and only on workloads that are sensitive to L3 cache. Otherwise, why would you add the extra L3 cache in the first place? We do believe that this might be the case for the SPEC CPU benchmarks, which AMD might be using to calculate said IPC improvements for the Bergamo and Siena announcements. Our tables are showing the IPC on all of the Zen 4 and Zen 4c cores being improved over the prior “Milan” Zen 3 cores at the same rate regardless of the L3 caches being different.

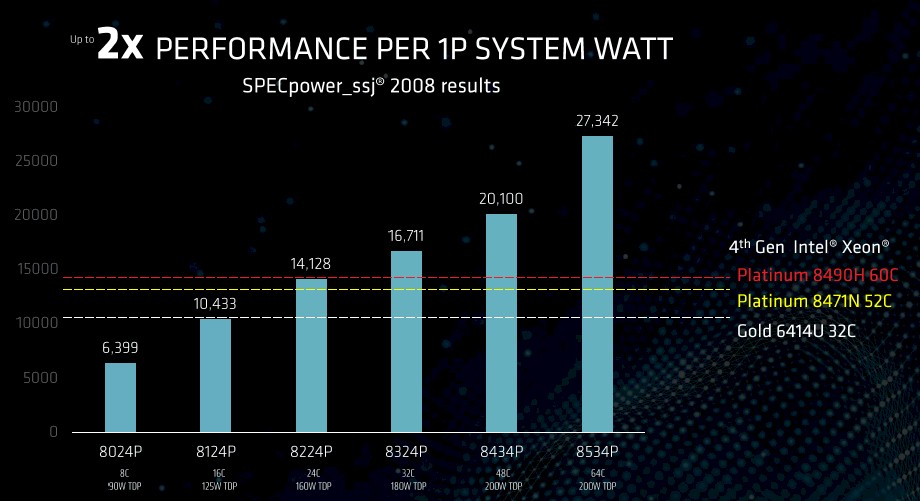

What matters, ultimately, is how the Siena chips stack up to the Intel Xeon SP alternatives, and here is how AMD is stacking up the Siena chips against the Intel Xeon SP chips:

We now await Intel’s “Sierra Forrest,” which seeks to compete against Bergamo and we think possibly Siena.

Nice product based on Bergamo core. Not unexpected.

That 8224P looks like a yummy lunchtime special for single-plate (1P) gastronomers, with the same fullfilling perf as dual-plate-capable 9224 dinner dish (at base deglutition speed), but just 4/9-th the price and 4/5-th the heat! And it seems as satisfying as servings of plate (-inum) dishes from the menus of competing hole-in-the-wall greasy spoons — get me a reservation! b^8