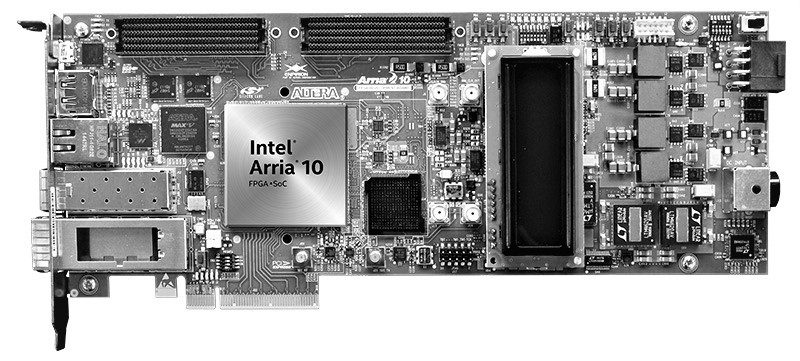

Intel FPGA Architecture Focuses on Deep Learning Inference

There has been much written about the potential for FPGAs to take a leadership role in accelerating deep learning but in practice, the hurdles of getting from concept to high performance hardware design are still taller than many AI shops are willing to scale, particularly when GPUs dominate in training and in a pinch, standard CPUs will do just fine for datacenter inference since they involve little developer overhead. …