AMD Widens Server CPU Line To Take Bites Out Of Intel, Arm

The best defense is a good offense, and as it turns out, the best offense is also a good offense. …

The best defense is a good offense, and as it turns out, the best offense is also a good offense. …

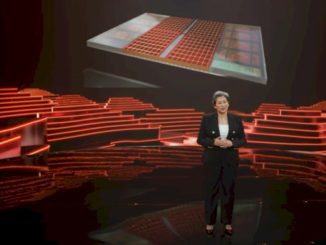

Let the era of 3D V-Cache in HPC begin.

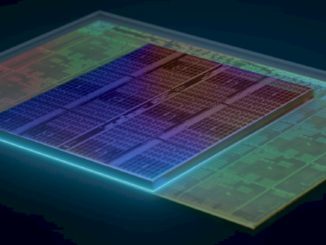

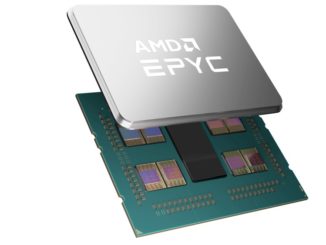

Inspired by the idea of AMD’s “Milan-X” Epyc 7003 processors with their 3D V-Cache stacked L3 cache memory and then propelled by actual benchmark tests pitting regular Milan CPUs against Milan-X processors using real-world and synthetic HPC applications, researchers at RIKEN Lab in Japan, where the “Fugaku” supercomputer based on Fujitsu’s impressive A64FX vectorized Arm server chip, have fired up a simulation of a hypothetical A64FX follow-on that could, in theory, be built in 2028 and provide nearly an order of magnitude more performance than the current A64FX. …

Last fall ahead of the SC21 supercomputing conference, AMD said it was going to be the first of the major compute engine makers to add 3D vertical L3 cache to its chips, in this case to variants of the “Milan” Epyc 7003 series of processors that debuted in March 2021 called the “Milan-X” chips. …

Necessity is the mother of invention, and advances in chip packaging are catching up to those in transistor design when it comes to working in three dimensions instead of the much more limited two. …

Designing a great CPU or GPU, or even an FPGA or a custom ASIC like a switch or router chip, is an important aspect of creating ever-more-powerful systems. …

All Content Copyright The Next Platform