As we are carefully watching here, there is a perfect storm brewing in the semiconductor space, both for manufacturers and system designers.

On the one hand, the impending demise of Moore’s Law presents a set of challenges—and opportunities—for emerging chip companies to arise and offer alternatives, often with customization cooked into the business model. And for end users, there is a rising tide of options that might lift a lot of boats if ecosystems are rapidly adopted. This is the case in the ARM space, as we’ve seen clearly this year, as well as for other architectures, including efforts from OpenPower, Sparc, and elsewhere.

Along the way, another, less noisy option (one that has existed for decades now) has been simmering away on the backburner. Not long ago, we explored what the future of open source might look like using the RISC-V ISA as an option. While the momentum there is still somewhat isolated, there are a few companies that are pushing the RISC-V Foundation’s work, including startup SiFive, which emerged from semi-stealth today, featuring a set of platforms that can address some custom silicon requirements for companies that don’t have the resources to engage in the long, expensive process of having their own custom chips brought to market.

One of the co-founders of SiFive is Krste Asanovic, who also serves as chief architect. For those who follow RISC-V, this is a familiar name as leads the RISC-V ISA work at UC Berkeley where the initial effort was launched. He is now also chairman of the RISC-V Foundation, although the developments at SiFive and the foundation are essentially separate. The company’s CTO, Yunsup Lee, who was another co-designer of the ISA and first microprocessors says that the time is right for open source hardware to find a place in the datacenter, although for this company’s customers, it is not necessarily as the CPU—at least, not yet.

“The semiconductor industry is at an important crossroads,” says Lee. “Moore’s Law has ended, and the traditional economic model of chip building no longer works. Unless you have tens, if not hundreds, of millions of dollars, it is simply impossible for smaller system designers to get a modern, high performance chip, much less one customized to unique requirements.”

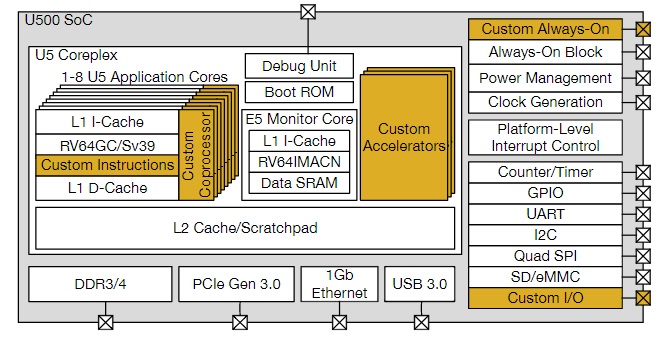

The company is rolling out its development boards (FPGA models of both of their SoCs—one for embedded applications (Freedom E300 series) and more important for the large-scale compute market, the Freedom U500 series (called Freedom Unleashed) which is a Linux-ready embedded RISC-V processor capable of 1.6 GHz with support for accelerators. The chips are built on 28 nm process from TSMC and is set to appeal to specific underserved markets, as Lee defines, which include machine learning, storage, and networking in particular.

Each of the SoCs can include a SiFIve U5 Coreplex with up to eight 64-bit RISC-V cores with both private and shared L2 caches and all the connections seen above. The key is that everything can be configured with a great deal of flexibility and extensibility with custom instruction set extensions, co-processors, custom accelerators and I/O as well as custom always-on blocks.

“The industry is trending towards companies that are looking for ways to justify costs. Using RISC-V and open source concepts that exist in software and applying that to hardware can reduce costs and time to market for underserved areas that are looking for custom silicon,” Jack Kang, another Berkeley alum who came from product roles at Nvidia and Marvell before joining the Sutter Ventures-backed startup. “Our differentiation is that we can customize this—it’s extensible. We can add instructions, accelerators and co-processors and there is high demand for that in some key underserved areas.”

To put the customization story in context, consider a use case in storage where many users have some unique cycle-hogging operations that standard CPUs can waste a lot of time performing. There, where there can be simple bit manipulations that take 10 instructions on an off-the-shelf CPU can have custom instruction replacements to do that in a single instruction—a 10X improvement for that part of the workload. While that is an attractive boost, few companies would think to invest the time and money to have something like that built, especially if they are smaller shops, Kang says.

While we will not be seeing this RISC-V approach take over the role of CPUs anytime soon from SiFIve since their focus is on the datacenter but as an accelerator for certain workflows that require customizations, there is still every reason to believe that RISC-V could have a lofty spot next to other architectures for building large-scale machines. The software ecosystem and partners touted by the RISC-V Foundation is growing—and attractive. But to truly get something off the ground beyond the use cases SiFive is serving takes a bottom-up approach. Like other semiconductor companies (and approaches like ARM) there is an initial push from the bottom before the top-level (datacenter) space can be reached. By starting with the microcontroller, embedded, and other markets, RISC-V can find more early adopters to enhance the base and build skyward from there.

“As far as RISC-V as the CPU in the datacenter, there is an opportunity for us eventually,” Kang says. “The general purpose architectures aren’t hitting the energy efficiency numbers and the need for customization is stronger than ever.”

Be the first to comment